在2月16日舉行的國際固態電路會議ISSCC上🕢,沐鸣徐鴻濤教授帶領的WiCAS(無線集成電路與系統)課題組在高性能CMOS數字功率放大器的設計方面再次發表研究突破🦸🏽♂️。該課題組在高性能CMOS功率放大器設計研究上提出了多項原創性技術,使高效率高功率的數字功率放大器更容易應用在寬帶無線通信上,相關成果已連續三年在國際固態電路會議上亮相(ISSCC 2018/2019/2020)👨🏽🦱。ISSCC是集成電路設計領域的國際頂級會議,是國際學術界和頂尖半導體公司的研發人員發布先進成果和最新進展的重要窗口,在國際半導體技術界具有重要的影響力。

功率放大器是無線系統的核心模塊,直接影響著整個系統的性能、功耗和成本。射頻前端芯片逐步與數字基帶芯片實現全集成,持續提升4G/5G/WiFi等無線技術的用戶體驗。但是隨著CMOS工藝向納米尺寸縮小🈚️,高襯底損耗、低電源電壓🧜♂️、低擊穿電壓等問題的不斷顯現👱🏻,使得高性能的CMOS功率放大器集成成為業界的研究難點,從而影響到了整個通信系統的電池壽命和封裝熱處理等方面。

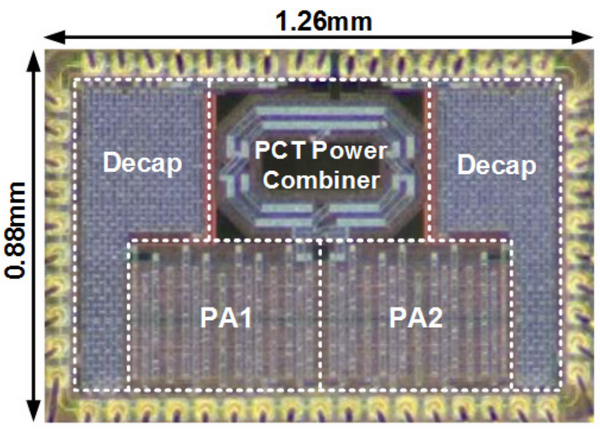

2018年💺,WiCAS課題組提出一種新型的數字式射頻功率合成技術💂🏿♂️,僅用約1平方毫米的芯片面積實現NBIOT雙頻帶功率合成(如下圖)🏋🏿♂️。另外✴️,借助數字化控製實現Doherty負載調製以提升回退效率,在效率曲線上實現了2個峰值(0/6dB)𓀇,相比於傳統功率放大器顯著提高了平均發射效率。該研究成果成功發表在ISSCC 2018會議上,該芯片以緊湊的芯片面積實現了近瓦級的輸出功率、雙頻帶覆蓋以及較高的平均發射效率🏊🏽♂️,特別適用於低成本的物聯網等無線通信應用場景。

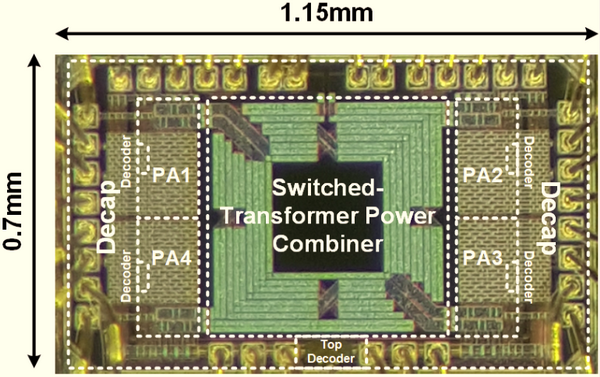

2019年,WiCAS課題組針對LTE、WLAN等寬帶應用的高峰均比和大動態範圍需求,進一步提出18dB深回退效率增強方案7️⃣,采用了新型的開關變壓器技術🕵🏼♀️,首次在效率曲線上實現了4個峰值(0/6/12/18dB),在不增加芯片成本的情況下,實現整體性能的提升👃🏻。該研究成果成功發表在ISSCC 2019會議上🌗,在40nm CMOS工藝上🫐,用1.1V單電源供電🔓,芯片面積僅0.8平方毫米(如下圖)。該成果為未來5G通信進一步提高集成度和能效提供了有力的技術支撐👩❤️💋👩。

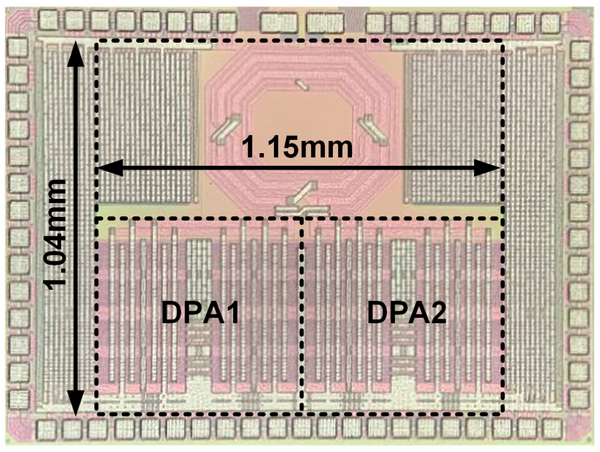

2020年🖖🏽,課題組針對更適合寬帶無線通信系統的笛卡爾架構,提出了一種基於變壓器合成的復數域負載調製方案,使笛卡爾功率放大器的輸出功率和效率達到了與極坐標架構相比擬的水平。在今年ISSCC 2020會議上發表的芯片,實現接近1瓦的峰值功率👳♂️,峰值效率43.1%🩱。在發射LTE信號時,芯片效率達24.4%🔳🛄,而且在不增加芯片成本和復雜度的前提下,該芯片實現了15bit高精度和大動態範圍,適用於5G、WLAN等寬帶通信系統👿👜。

未來☯️,該研究團隊將進一步開展超寬帶、高效率、高線性度功率放大器的研究應用,繼續與學術界和產業界夥伴合作,努力實現數字式功率放大器的產業化🎚🦸🏻♂️、實用化,方便未來快速低成本地集成到單片全集成收發機中,有助於推動未來5G通信的快速發展。