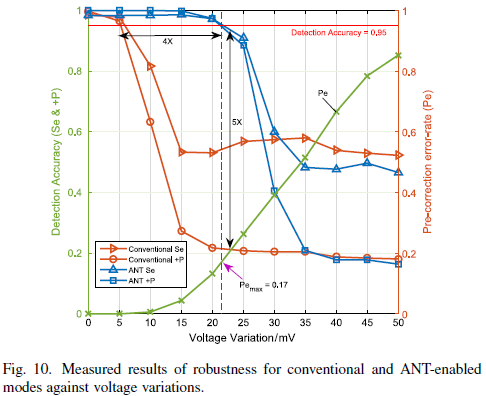

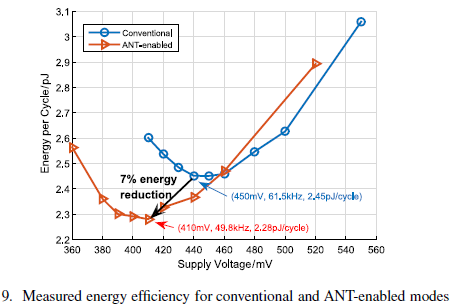

實驗室曾曉洋教授課題組在亞閾值可容錯ECG處理器研究中◼️,提出了基於加權均值雙邊預測的ANT(Algorithmic Noise Tolerance)技術和兩級異構容錯方案。提出的ANT方法通過在信號的預測窗口中提升可信樣本的權重,而降低未驗證樣本的權重,從而提高估計準確度。基於所提出的容錯技術,設計實現了一款低電壓🏊🏿、可容錯的心電信號處理芯片👸🏻。該ECG 信號處理芯片共有三級流水線🦼,第一級是小波濾波器組,第二級和第三級是 GLRT 模塊。容錯電路的第一級采用基於影子寄存器技術的時序檢測鏈👵,來監控電路的時序錯誤,容錯電路的第二級采用基於比較器的檢錯機製,兩級檢錯電路都使用了一個預測長度為 4 的加權均值雙邊預測估計器🫴, 估計器的系數通過實驗確定,並且為了節省硬件面積和功耗開銷,選擇 m/8 或者 n/16 作為系數, m 和 n 為整數🗜,因為這些系數可以通過移位和加法實現。流片結果表明,該心電信號處理電路的ANT模塊只占主幹電路5%的面積🧖🏻♂️,可在電壓過縮放條件下容納17%的錯誤率,實現低電壓工作(可低至0.41V),能效(energy/cycle)可達到2.28pJ🦻。

成果相關論文“An Area-Efficient Error-Resilient Ultralow-Power Subthreshold ECG Processor”發表在IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II-EXPRESS BRIEFS上。