在數字集成電路設計特別是基於FPGA的電路設計領域,越來越多的設計工程師開始使用高層次綜合(High-levelSynthesis工具進行設計⏳。高層次綜合技術將電路設計抽象層次從當前的寄存器傳輸級(RegisterTransferLevel)提升到了C/C++🤞🏿、SystemC等更高的抽象層。電路設計者只需要利用C/C++或SystemC對電路進行描述,高層次綜合工具自動將這些描述文件轉換成高效的寄存器傳輸級描述文件。因此電路設計者可以從復雜繁瑣的寄存器傳輸級設計中解脫出來👘,將更多的精力放在系統整體性能的優化上🫒,從而大大提高了設計效率🦛。

然而目前高層次綜合工具所生成的寄存器傳輸級電路描述的質量與電路設計專家手工設計的電路描述相比仍然存在著較大的差距⛹🏽♀️。其中的主要原因之一在於目前的高層次綜合工具往往無法根據電路的C/C++🦸🏼♂️、SystemC描述文件🐲,綜合出高效的存儲器子系統👙。存儲器存取性能和處理器運算性能之間的差距越來越大,使得在一個電路系統中,存儲器子系統往往成為整個系統的性能瓶頸。因此綜合出高效的存儲子系統對高層次綜合工具至關重要😮。

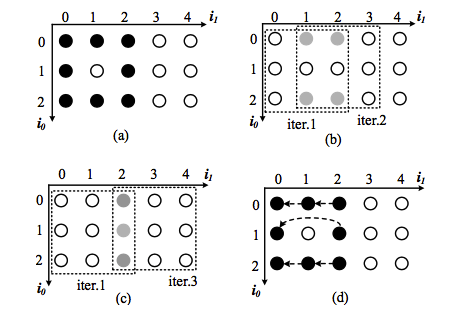

針對存儲器並行訪問需求和存儲器帶寬有限之間的矛盾,實驗室曾璇教授課題組提出了一個基於數據復用的存儲器劃分算法。該算法首先利用循環變換技術對源代碼進行等價變換,提高代碼數據復用性💁🏻♂️,然後利用一個數據復用策略將可復用的數據緩存在被組織成為寄存器鏈的片上寄存器中。該算法利用一個存儲器劃分策略將原存儲陣列劃分到多個不同的存儲器塊中,並將不能復用數據的存儲器訪問分別映射到這些存儲器塊上,從而使得這些存儲器訪問可以同時訪問數據💹。與現有的存儲器劃分算法相比,對於大部分在圖像視頻處理和科學計算領域的應用來說,實驗室所提出的劃分算法在算法復雜度、硬件資源和功耗開銷方面都具有很大的優勢。

實驗結果表明,所提出的算法執行時間少於一毫秒🧓🏻,可以將需要的存儲塊數目平均減少了59.7%𓀙🌰,查找表數量平均減少了78.2%,觸發器數量平均減少了65.5%,DSP48E數量則平均減少了59.7%,同時將整個存儲器系統的動態功耗平均降低了74.8%🧕🏽🧑🏼🍼。論文2017年被IEEETransactionsonComputer-AidedDesignofIntegratedCircuitsandSystems接收👮🏻♂️。

(a)PREWITT 圖像濾波核的訪存模式 (b)相鄰迭代間的數據復用

(c)第一個迭代和第三個迭代之間的數據復用 (d)數據復用鏈